I display TFT (Thin-Film-Transistor) sono oggi onnipresenti e trovano impiego in un numero sempre maggiore di applicazioni. Se fino a poco tempo fa un display a cristalli liquidi (LCD) o GLCD (graphic LCD) era sufficiente per la maggior parte delle applicazioni embedded, oggi le richieste e le aspettative degli utenti sono più elevate e gli ingegneri elettronici devono tenere il passo incorporando tecnologie più complesse nei loro prodotti per rimanere competitivi. La tecnologia dei display è complessa e questo articolo non intende entrare nei dettagli di ogni aspetto, ma piuttosto fornire una panoramica pratica di livello relativamente alto.

Come funzionano i TFT

A rischio di dire cose ovvie, i display TFT sono costituiti da una griglia di pixel che vengono utilizzati per visualizzare un’immagine.

Pixel in una griglia.

È la stessa cosa dei GLCD, con la differenza che i TFT sono a colori anziché monocromatici. Per produrre un’immagine a colori, ogni pixel è composto da sub-pixel rossi, verdi e blu (i colori primari della luce); la luminosità di ogni sub-pixel può essere controllata individualmente e, quando i sub-pixel sono visti da una distanza sufficiente, si combinano per apparire come un singolo pixel di un determinato colore. Con i TFT, i transistor che controllano i pixel sono incorporati all’interno dei pixel stessi (anziché essere inseriti in un circuito di controllo esterno) e questo consente, tra gli altri vantaggi, una velocità di aggiornamento elevata e un controllo preciso della luminosità (gli svantaggi sono il costo e il consumo energetico più elevati).

Dietro la matrice TFT c’è una retroilluminazione e ogni sub-pixel agisce come una sorta di “finestra-cieca” che lascia passare la luce o la blocca. La “finestra-cieca” è costituita da un cristallo liquido inserito tra due filtri polarizzanti ortogonali; il cristallo liquido assiste la luce o la blocca dal passaggio attraverso i filtri, a seconda della tensione applicata. Ogni sub-pixel è inoltre dotato di un filtro colorato che gli conferisce il colore rosso, verde o blu.

Driver del TFT

La matrice di pixel (sub-pixel) nel TFT è controllata da una linea (filo) per ogni riga e ogni colonna. All’interno del TFT si trova un chip di controllo (ad esempio, ILI6480, HX8257A, ILI9341) che è collegato alle sue uscite a ciascuna riga e a ciascuna colonna della matrice di pixel (sub-pixel). Poiché i TFT sono a “matrice attiva” (anziché a “matrice passiva”), i pixel devono essere costantemente aggiornati per mantenere la visualizzazione (i pixel in un display a “matrice passiva” mantengono la loro impostazione fino a quando non viene impostato diversamente).

A seconda del chip del driver, questo avrà una o più interfacce di ingresso.

Interfaccia RGB parallela

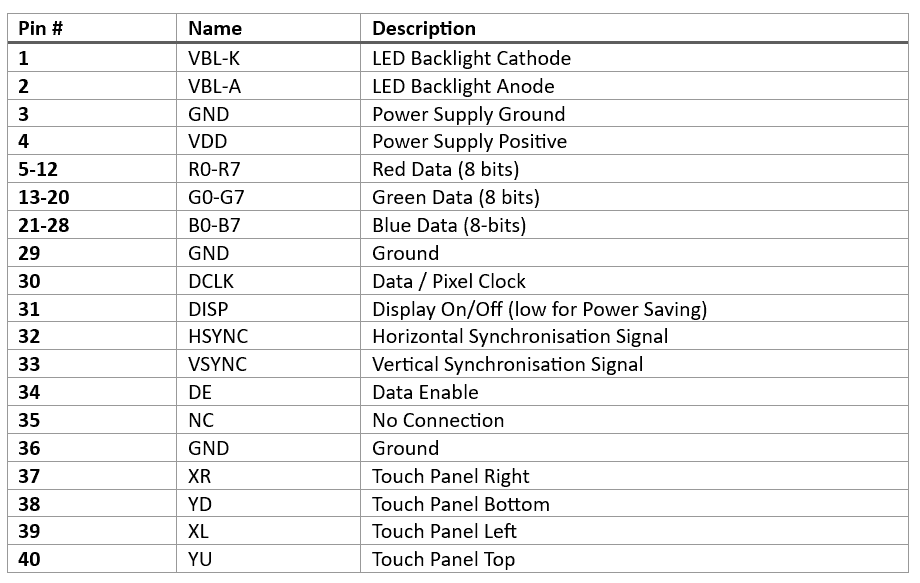

Forse una delle interfacce di ingresso più comuni nelle applicazioni embedded è l’interfaccia parallela RGB. Di seguito è riportato un esempio di piedinatura per un’interfaccia RGB parallela a 40 pin:

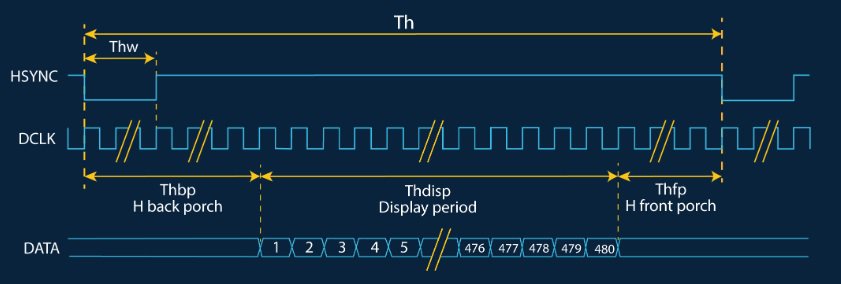

Ogni pixel ha 8 bit di dati per ciascuno dei canali rosso, verde e blu (per un totale di 24 bit). Per il clock dei dati viene utilizzato un pixel clock, un segnale di sincronizzazione verticale per indicare l’inizio/la fine di un fotogramma completo e un segnale di sincronizzazione orizzontale per indicare l’inizio/la fine di ogni riga.

La velocità (frequenza) del Pixel Clock determina il tempo necessario per disegnare ogni fotogramma e quindi la frequenza dei fotogrammi (frame rate).

I segnali di sincronizzazione orizzontale e verticale avranno normalmente impulsi di durata molto maggiore rispetto al Pixel Clock, creando i cosiddetti “portici anteriori e posteriori” per le linee HSYNC e VSYNC.

Gli intervalli di valori validi per ciascuno di questi parametri sono normalmente inclusi nella scheda tecnica (datasheet) del display.

L’interfaccia deve essere costantemente pilotata e aggiornata, altrimenti il display si oscura.

I dati RGB paralleli per il display possono essere a loro volta generati da un altro chip driver, come la serie di controller per display SSD1963 (interfaccia di ingresso parallela separata) o FT8xx (interfaccia SPI/I2C); oppure alcune MCU / MPU dispongono di periferiche in grado di emettere direttamente i dati RGB paralleli (e i segnali di clock / sincronizzazione associati).

Interfaccia SPI/I2C/UART

Alcuni chip driver (ad esempio, ILI9341) dispongono di un’interfaccia di comunicazione seriale (come SPI/I2C/UART) che può essere utilizzata per controllare il display. Il protocollo varia da chip a chip e di solito sono disponibili librerie software di accompagnamento per disegnare testo / grafica / ecc. sul display. Poiché la velocità massima di queste interfacce seriali è relativamente bassa, l’aggiornamento del display può richiedere un certo tempo e sono più adatte ad applicazioni in cui solo piccole sezioni dello schermo devono essere aggiornate regolarmente (ad esempio, il testo della lettura di un sensore); non sono invece adatte ad applicazioni in cui il contenuto di ampie regioni dello schermo deve cambiare rapidamente (ad esempio, la riproduzione di video).

MIPI-DSI

La “Mobile Industry Processor Interface” Alliance “Display Serial Interface” è un’interfaccia di comunicazione per schermi basata sulla segnalazione a coppie differenziali. Esiste una coppia differenziale “clock” e una o più coppie differenziali “dati”. Grazie all’utilizzo di coppie differenziali, le velocità di clock possono essere dell’ordine dei GHz, mentre le EMI sono ridotte e l’immunità alle interferenze è elevata). Grazie all’elevata velocità e alla possibilità di aggiungere altre corsie di dati per aumentare il throughput dei dati, il MIPI-DSI è particolarmente adatto agli schermi ad alta risoluzione più grandi, dove il throughput dell’interfaccia parallela RGB non è più sufficiente (al di sopra di circa 1024×768). MIPI-DSI è utilizzato nel popolare RaspberryPi.

Integrazione

Quando si avvia un progetto che prevede l’integrazione di un TFT, è necessario considerare una serie di fattori quali:

- Dimensione e risoluzione del display richiesto.

- Velocità di aggiornamento (refresh rate) / throughput richiesto.

- 28Microcontrollore/microprocessore utilizzato, periferiche disponibili e potenza/velocità di elaborazione.

Le MCU/MPU più potenti dispongono spesso di periferiche in grado di pilotare direttamente i TFT. Se non sono richieste velocità di aggiornamento elevate o se solo una piccola regione dello schermo viene aggiornata regolarmente, può essere sufficiente un display con interfaccia SPI/I2C/UART. Per i processori più piccoli e meno potenti sono disponibili diversi operatori del settore che offrono soluzioni di visualizzazione semplificate in cui un chip di processore grafico dedicato intermedio gestisce il display, come 4D Systems / Nextion / FT8xx EVE / ecc.

Proteus include un modello di display ILI9341, che può essere utilizzato per sperimentare un display TFT in simulazione.

Puoi scaricare la versione demo di Proteus di Labcenter, distribuito in Italia da Galgo Electronics.

Articolo di Dane du Plooy – eiTech Systems – All content Copyright Labcenter Electronics Ltd. 2024 – Per l’articolo originale clicca qui