Libera nuovi livelli di prestazioni di calcolo con il vertical power delivery

By Ajith Jain, Vice President HPC Business Unit

Man mano che i livelli di potenza dei processori per AI ad alte prestazioni continuano ad aumentare e le tensioni del core a diminuire grazie a nodi di processo avanzati, i progettisti di sistemi di potenza sono chiamati a gestire l’aumento di impedenza e le cadute di tensione nei power delivery network (PDN), gradienti di tensione attraverso pin di potenza di processori ad elevata corrente e bassa tensione, specifiche di prestazioni transienti e perdite di potenza.

Nel caso del cluster computing, in cui array di processori, molto vicini tra loro, vengono utilizzati per aumentare la velocità e le prestazioni dell’apprendimento automatico, la complessità PDN aumenta in modo significativo poiché l’erogazione di corrente deve essere eseguita verticalmente da sotto l’array.

La progettazione di un PDN utilizzando l’architettura Vicor Factorized Power Architecture (FPA™) con i moltiplicatori di corrente sul point-of-load invece delle tradizionali tecniche di conversione della tensione, consente un significativo incremento di prestazioni. Ciò è reso possibile dalle caratteristiche dei componenti di potenza del punto di carico (PoL): elevata densità di corrente, ridotto numero di componenti e, cosa molto importante, flessibilità nel posizionamento. I componenti di potenza PoL consentono quindi di erogare corrente lateralmente e/o verticalmente ai core del processore AI e circuiti della memoria, riducendo significativamente le impedenze del PDN.

Comprendere le esigenze di correnti di picco con le attuali power delivery network

Le moderne GPU hanno decine di miliardi di transistor, un numero che cresce ad ogni nuova generazione e famiglia di prodotti, e che è reso possibile da geometrie di nodi di processo sempre più piccole. Seguono poi miglioramenti nelle prestazioni del processore ad ogni nuova generazione, ma tutto questo ha un prezzo, ovvero la richiesta di erogazione di potenza che, va aumentando, esponenzialmente.

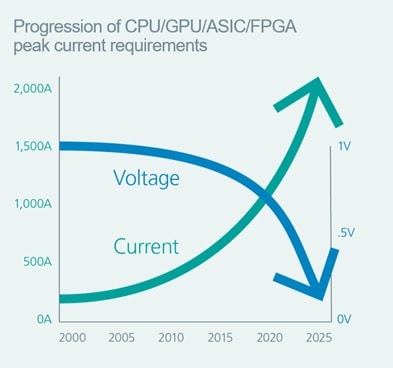

La Figura 1 mostra il drammatico aumento dei requisiti di corrente a causa della ridotta geometria dei transistor e delle tensioni del core.

Figura 1 — Nella maggior parte dei casi, l’erogazione della potenza è ora il fattore limitante nelle prestazioni di calcolo poiché i nuovi processori consumano correnti sempre crescenti. La fornitura di energia comporta non solo la distribuzione della potenza, ma anche l’efficienza, le dimensioni, i costi e le prestazioni termiche.

Le richieste di correnti di picco fino a 2000A sono ora un requisito tipico. In risposta a questa sfida di erogazione di energia, alcune società xPU stanno valutando opzioni multi-rail in cui i principali rail di alimentazione dei core sono divise in cinque o più ingressi di minore corrente. Il PDN per ciascuno di questi rail deve comunque erogare una corrente elevata, pur avendo bisogno di una precisa regolazione individuale, il che mette una certa pressione sulla densità del PDN e sulla sua posizione fisica sulla scheda dell’acceleratore.

Per aumentare ulteriormente questa complessità, la natura altamente dinamica dei carichi di lavoro dell’apprendimento automatico si traduce in transienti di/dt molto elevati che durano diversi microsecondi. Ciò crea stress attraverso il PDN di un modulo processore ad alte prestazioni o scheda acceleratrice.

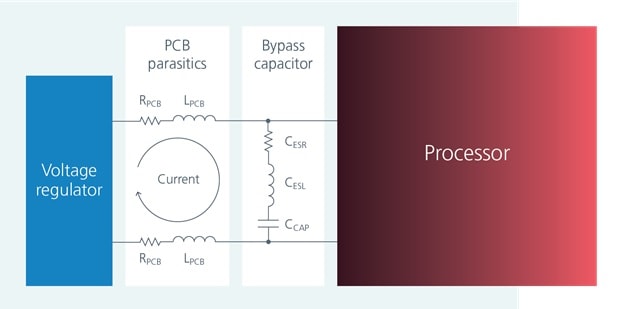

L’architettura di una tipica power delivery network è evidenziata nella Figura 2.

Figura 2 — Tipica PDN per processore ad elevate prestazioni

Le migliori pratiche per ottimizzare una power delivery network

Il lavoro del consorzio Open Compute Project® (OCP®) ha contribuito a stabilire un quadro standard per la progettazione di sviluppo di processori rack-based e card-based. L’Open Rack Standard V2.2 definisce un server backplane 48V e una tensione operativa di 48V per gli open accelerator modules (OAM) utilizzati prevalentemente per i carichi di lavoro di intelligenza artificiale (AI) e machine learning. Per mantenere la compatibilità con i sistemi 12V antecedenti, lo standard prevede la capacità di soddisfare requisiti 12-to-48V e 48-to-12V.

Il concentrarsi sull’alimentazione del processore, o PoL, è pieno di sfide tecniche. I progressi tecnici evidenziati nella sezione precedente si sono concentrati sulla tendenza al ribasso del ridimensionamento della tensione, sugli stretti requisiti nella tolleranza di tensione del core e sulla tendenza al rialzo del consumo di corrente. A livello della scheda, l’impatto di questi fattori si manifesta in più modi.

Le densità di corrente di picco riscontrate sono estreme per qualsiasi PCB. Percorsi di instradamento della potenza capaci di questi carichi enormi richiede attenzione. I carichi di lavoro altamente dinamici possono creare tensioni transienti di spiking, che i processori sofisticati trovano dannosi e potenzialmente distruttivi. Tuttavia, una scheda processore ha centinaia di altri componenti passivi, memoria e altri IC essenziali per il suo funzionamento che necessitano anch’ essi di posizionamento.

Poi ci sono le perdite di I2R. Le lunghezze delle piste per il percorso di alimentazione devono essere brevi. Per ottenere questo risultato, i moduli di conversione di potenza devono essere vicini al processore per ridurre il riscaldamento della pista. La probabilità che si verifichino delle flessioni del PCB dovute alle correnti di carico del processore e ai gradienti termici localizzati richiede degli irrigidimenti della scheda del processore. Inoltre, le specifiche di efficienza energetica del convertitore dovrebbero essere il più elevate possibile per evitare ulteriori problemi di gestione termica.

Libera la potenza del processore

Fornire sufficiente potenza al processore oggi richiede innovazione per cercare di superare lo status quo. Nuove idee, architetture, topologie e tecnologie sono la strada per una rete di distribuzione della potenza più affidabile e scalabile. La Factorized Power Architecture (FPA™) di Vicor è la base per fornire una potenza più efficiente per le esigenze odierne di calcolo ad elevate prestazioni senza precedenti.

Figura 3 — Factorized Power Architecture (FPA™) fattorizza la potenza nelle funzioni dedicate di regolazione e trasformazione. Entrambe queste funzioni possono essere ottimizzate e implementate singolarmente per fornire una soluzione ad alta densità e ad alta efficienza.

L’FPA di Vicor suddivide il compito di un convertitore di potenza nelle funzioni dedicate di regolazione e trasformazione. Una soluzione ad alta efficienza e ad alta densità si ottiene separandoli ed ottimizzandoli singolarmente. L’FPA in combinazione con la topologia Sine Amplitude Converter (SAC™) è alla base di diverse architetture innovative che possono aiutare a liberare tutta la potenza dei processori ad alte prestazioni di oggi.

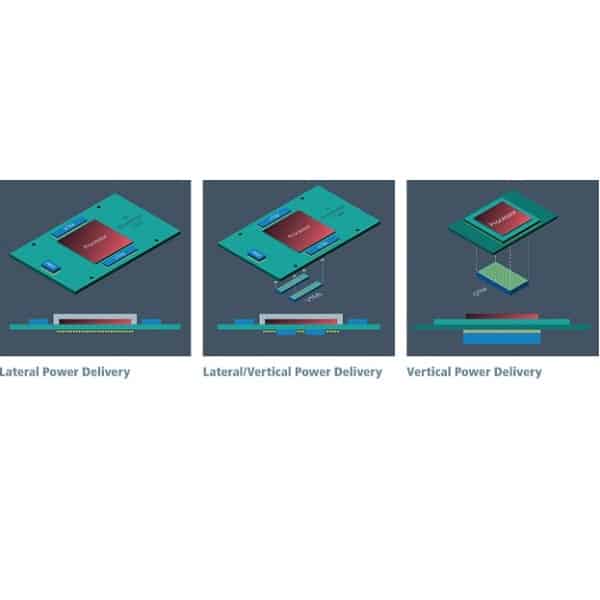

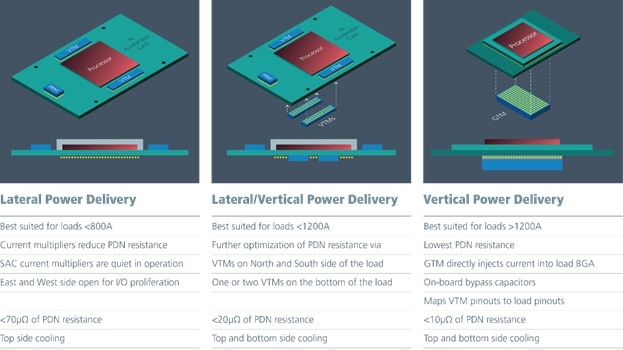

Figura 4 — Sfruttando l’FPA, Vicor riduce al minimo le resistenze “ultimo pollice” con diverse soluzioni brevettate che coinvolgono la lateral power delivery (LPD) e la vertical power delivery (VPD). Tutti consentono ai processori di raggiungere livelli di prestazioni in precedenza irraggiungibili per supportare le attuali richieste di elaborazione HPC, in crescita esponenziale.

La tecnologia dei convertitori di potenza Vicor sfrutta l’eccezionale Factorized Power Architecture che non solo ottimizza l’efficienza del convertitore di potenza, ma consente anche perdite PDN molto basse associate ad una erogazione di potenza a corrente elevata e bassa tensione al PoL (ASIC o una CPU o una GPU ecc.).

La Lateral power delivery è una tecnica innovativa in cui i due moltiplicatori di corrente (moduli Vicor VTM™) si affiancano al lato nord e sud o il lato est e ovest del processore. Questa tecnica è preferibile per correnti di carico di ~800A a 0,8V nominali con associati 70µΩ di PDN a 100°C. Usando questi numeri, possiamo calcolare ~45W di perdita di potenza. Un dissipatore di calore che copra sia i moltiplicatori di corrente alti 2,8 mm che il processore come mostrato nella figura sarebbe una buona soluzione termica. Questa architettura è eccellente per alimentare schede grafiche acceleratrici (OAM o altro), ASIC e APU di rete utilizzati in data center hyperscale o cabinet di supercomputer.

La tecnica Lateral-vertical power delivery è simile alla lateral power delivery, ma con una differenza: solo il 70% della potenza viene erogata lateralmente utilizzando i moltiplicatori di corrente affiancati ai lati del processore. Un ulteriore moltiplicatore di corrente sul lato inferiore del processore erogherà il restante 30% della corrente di carico direttamente al processore BGA. L’ibrido tra laterale e verticale raggiunge una riduzione della perdita PDN di quasi un fattore quattro! Questa tecnica libera anche spazio sulla scheda per accogliere un secondo rail ad elevata corrente (aux) o rail di memoria HBM sul lato superiore della scheda attorno al processore.

La Vertical-lateral power delivery, invece, sfrutta il vantaggio di spingere il 50% della corrente di carico attraverso ulteriori moltiplicatori di corrente sul lato inferiore del processore. Questa tecnica consente un’ulteriore riduzione del 50% della perdita PDN rispetto all’approccio verticale laterale. Un progetto da 1200A può ora realizzare una resistenza PDN di soli 10µΩ, con conseguente perdita di potenza inferiore a 14,4W. In questo Caso il dissipatore può essere posizionato su entrambe le superfici superiore ed inferiore del carico se lo spazio lo permette. Questa architettura è particolarmente efficace per applicazioni che non possono accettare componenti sul lato superiore della scheda per facilitare l’interconnessione dei segnali veloci dalla periferia dell’ASIC. Esempi ne sono CPO, NPO e dispositivi di comunicazione rete/banda larga.

La vertical power delivery è la soluzione ideale in termini di erogazione di correnti molto elevate alle basse tensioni del core del processore con la più bassa resistenza PDN. In questo caso, i moltiplicatori di corrente e i condensatori di bypass sono sovrapposti l’uno sull’altro per formare un modulo di potenza integrato (geared current multiplier) che può essere montato direttamente sotto il processore spostando il banco di condensatori di bypass. I GCM Vicor sono dispositivi costruiti su misura che mappano la piedinatura del moltiplicatore di corrente al processore di AI BGA, oltre a essere in grado di fornire tutti i condensatori di bypass necessari all’interno del modulo stesso. Questa tecnica apre il piano superiore del PCB per l’instradamento di segnali ad alta velocità dalla periferia del processore per realizzare una soluzione con la massima integrità del segnale. Applicazioni come CPO (Package che ospita processori ottici e di rete) e ASIC per segnali ad alta velocità possono trarre vantaggio da questa tecnica di erogazione di potenza.

Le architetture Vicor sono abbastanza flessibili da poter essere adattate a un’ampia varietà di soluzioni di calcolo ad alte prestazioni. Le soluzioni Vicor possono ridurre le resistenze della scheda madre fino a 50 volte e il conteggio dei pin di potenza di elaborazione di oltre 10. Sfruttando un’architettura di potenza fattorizzata (FPA™), Vicor riduce al minimo le resistenze “ultimo pollice” con soluzioni brevettate che combinano lateral power delivery (LPD) e vertical power delivery (VPD). Entrambe consentono ai processori di raggiungere livelli di prestazioni precedentemente irraggiungibili per supportare le attuali richieste di elaborazione HPC, in crescita esponenziale.

Le architetture FPA non hanno eguali nella densità di corrente e nella riduzione delle perdite di potenza attraverso PDN. Le architetture corrette, le topologie e le dimensioni ridotte dei moduli sono uniche nel settore energetico e, affinché i processori di prossima generazione funzionino a piena capacità, hanno bisogno di soluzioni di alimentazione in grado di adattarsi, scalare e fornire potenza ad alta densità. Moduli di potenza robusti e affidabili insieme a topologie innovative sono essenziali in un sistema dinamico in cui i requisiti di potenza cambiano rapidamente. L’intelligenza artificiale, l’apprendimento automatico e l’edge computing non disporranno mai di abbastanza potenza per il domani utilizzando le architetture di alimentazione tradizionali. Per soddisfare questo bisogno continuo è necessario innovare oggi ed essere pronti ad adattarsi e scalare per il domani utilizzando la potenza modulare.

Per informazioni clicca qui

Open Compute Project e OCP sono marchi industriali registrati di Open Compute Project.

FPA™ è un marchio industriale di Vicor Corporation