by Lee Morgan, Tektronix

Quando si analizza la sorgente del Jitter sul segnale dati, a volte è possibile non riuscire ad individuarne la causa nel layout. Il passo successivo è generalmente quello di verificare una possibile influenza sulle lane dati da parte delle linee di alimentazione, anche dette “power rail”. Sia il jitter che le linee di alimentazione vanno studiate nei due domini, tempo e frequenza. Se si mette a confronto il cosiddetto jitter periodico PJ e le sue component spettrali con le spurie relative al ripple sulle linee di alimentazione, si possono osservare correlazioni interessanti. La cosiddetta PDN (Power Distribution Network) può infatti impattare l’integrità del segnale sulle linee dati.

Il Jitter normalmente si misura in relazione al clock del sistema; se il clock viene “integrato” nel segnale seriale trasmesso per poi essere successivamente riestratto dal ricevitore, è essenziale valutare il segnale elettrico con l’oscilloscopio in modo da utilizzare lo stesso come strumento di estrazione del clock dal segnale dati misurato.

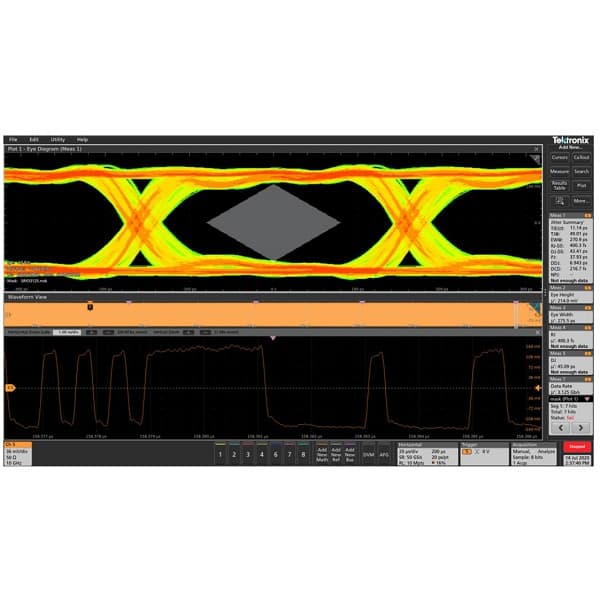

Figura 1: Diagramma ad occhio con mask test, in alto, e forma d’onda corrispondente, in basso.

L’impatto sugli errori della Signal integrity e della Power Integrity

Jitter e rumore, purtroppo, sono fonte di errori. Il rumore impatta in maniera generica sulla ampiezza del segnale sovrapponendosi, mentre il jitter produce variazioni sulla temporizzazione del segnale in particolare quando avviene una transizione del bit informativo. Anche il rumore impatta sul jitter, producendo distorsioni di fase oltre che di ampiezza. Quando il rumore diventa jitter, si hanno i cosiddetti problemi di crosstalk, rumore randomico e anche impatti di natura elettromagnetica o EMI.

Quando ci si concentra sulla Signal integrity, si focalizza l’analisi sulle prestazioni del trasmettitore, sul clock di riferimento, sulla natura del canale trasmissivo e infine sul ricevitore. Il tutto si valuta in termini di BER, ovvero di Bit Error Rate. La Power integrity invece si riferisce alla capacità della linea di alimentazione di fornire un segnale di tensione il più possibile stabile e ad evitare loop su percorsi a bassa impedenza che possono venirsi a creare nel circuito.

SI e PI sono indissolubilmente legate l’una all’altra. Le power rail o PDN, possono provocare rumore addizionale e jitter mentre il design del PCB e i componenti stessi (package, pin, tracce, vias, connettori etc…) possono impattare sulla impedenza della lane, e dunque sul carico applicato alla linea di alimentazione.

JITTER E POWER DISTRIBUTION NETWORK

Se le Power Distribution Network debbono occuparsi di garantire una tensione costante sul circuito e di alimentare con sufficiente corrente i vari componenti attivi presenti nel design, il loro impatto è determinante sia sui componenti attivi che su quelli passivi.

La Power Distribution Network è infatti da considerarsi come il sistema completo, non soltanto il regolatore di tensione e le linee di alimentazione dei chipset, ma tutte le interconnessioni, le vias, e la componentistica collegata inclusi adattatori e ball-grids. Tutto contribuisce alla impedenza serie equivalente che il SERDES deve saper gestire (le cosiddette impedenze equivalenti ESR, ESC, e ESL ovvero resistiva, capacitiva e induttiva).

PJ E GROUND BOUNCE

Il rumore sulle Power rail, che si manifesta sotto forma di un “ripple”, generalmente non supera qualche millivolt di ampiezza. Attuare misure accurate su questa scala e per frequenze fino al GHz impone l’utilizzo di sonde speciali, che abbiamo ampia banda passante ed elevata impedenza in DC ma che si comportino come linee trasmissive a 50 Ω per le alte frequenze. Si tratta di sonde progettate specificamente per avere un comportamento di questo tipo. Utilizzandole in combinazione con un oscilloscopio dotato del pacchetto di misure automatiche è possibile investigare il comportamento delle power rail e anche rilevare i parametri legati alle misure di jtter (TIE, RJ, DJ, PJ).

Gli alimentatori di tipo switching sono in grado di regolare la tensione tra la “rail” e il ground (o meglio al cammino circuitale di ritorno verso il ground). Trattandosi di alimentatori switching per definizione passano da uno stato on ad uno stato off in successione mantenendo costante la tensione d’uscita mediante regolazione del duty cycle. Questi alimentatori evitano accuratamente qualsiasi condizione di alta dissipazione e pertanto consumano meno di un alimentatore di tipo lineare. Per contro, queste continue commutazione che ne determinano il principio di funzionamento si traducono purtroppo in rumore di commutazione o switching noise che è causa tipicamente di un jitter di tipo periodico (PJ) sul segnale.

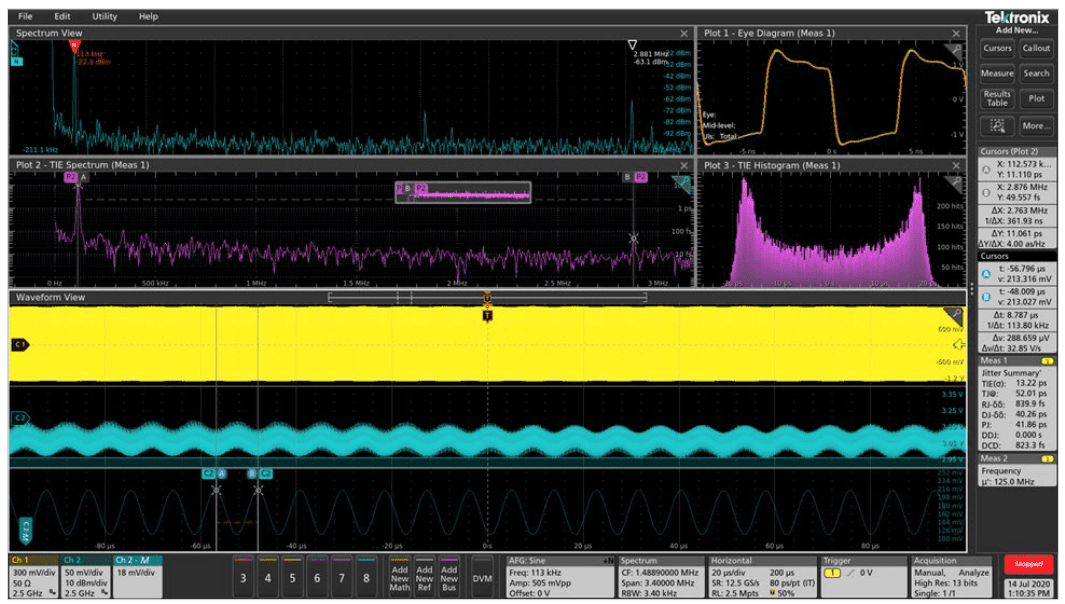

La commutazione, infatti, avviene a frequenza fissa il cui valore VRM viene indicato nel datasheet. Una possibile correlazione tra lo spettro in frequenza del ripple suddetto (in alto a sinistra nella Figura 2) e quello dello spettro del TIE del segnale (Time Interval Error (stessa figura, appena sotto), consente di verificare eventuali sovrapposizioni delle spurie e pertanto collegare causa ed effetto con una misura oggettiva, Il market rosso in Figura 2 è piuttosto indicativo ed esplicativo di quanto abbiamo ora affermato,, L’istogramma del TIE a destra presenta una cosiddetta “firma” con profilo a sella di cavallo, indicativo di un jitter sinusoidale.

Figura 2: Spettro del ripple della power rail in alto a sinistra e spettro TIE appena sotto di esso, insieme al segnale e alle forme d’onda della power rail e all’istogramma TIE.

L’alimentatore può introdurre anche rumore randomico, contribuendo alla componente RJ del jitter. La figura 2 lo mette in risalto come un rumore di fondo dello spettro visualizzato tramite la funzione Spectrum View dell’oscilloscopio. In questo caso ad esempio il rumore randomico dovuto al ripple è piuttosto basso e contribuisce al jitter randomico RJ soltanto per 0.84 ps.

PJ E IL “GROUND BOUNCE”

Durante una commutazione di stato logico del segnale, i trasmettitori e ricevitori assorbono o rilasciano energia verso la PDN. Quando la commutazione avviene per numerose lane e segnali simultaneamente, l’impatto sulla linea di alimentazione e sulla linea di ground può essere significativo. In poco tempo si introduce o si sottrae una densità di carica dalla power rail o dal piano di massa tale da alterare il livello di tensione. La variazione di tensione può manifestarsi nel cosiddetto ground bounce e nel simultaneo switching noise (SSN). In sostanza quella lane che dovremmo considerare come riferimento comune di tensione o percorso di ritorno della corrente e che dovrebbe stare a zero volt, si trova a gestire una iniezione o sottrazione di carica.

Il Dimultaneous Switching Noise SSN si manifesta come qualcosa di randomico nel dominio del tempo, ma non in quello della frequenza. Infatti, se lo spettro del segnale relativo alla linea dati risulta composto dalla frequenza fondamentale (di Nyquist) e da alcune armoniche multiple (in genere un paio), con al più le sub armoniche relative a sequenze di bit identici e contigui, lo spettro del SSN risulta periodico con moltissime spurie di piccola ampiezza a causare un jitter periodico PJ.

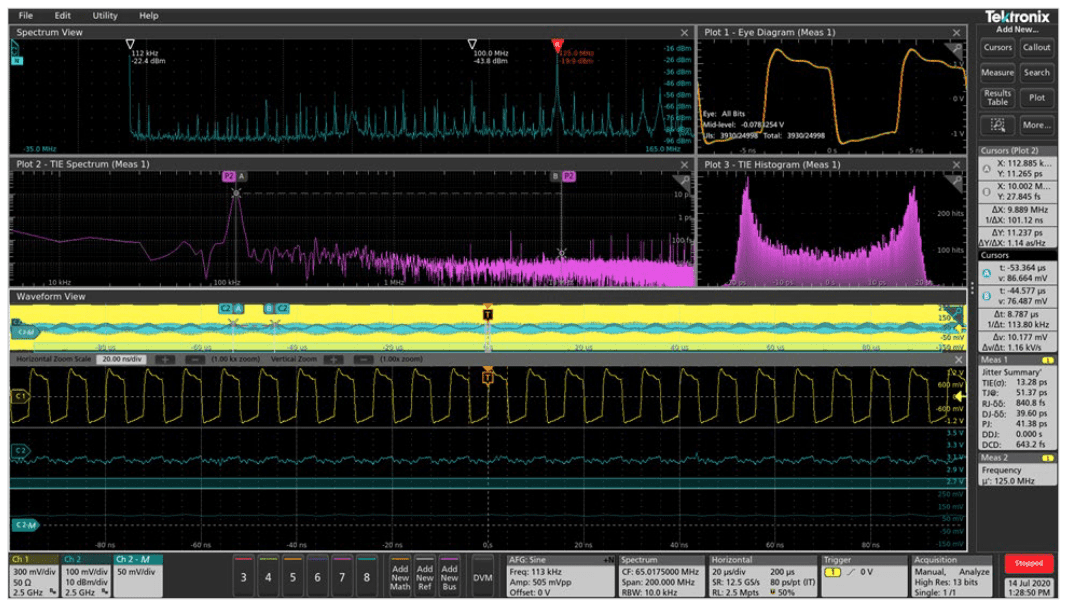

A conferma del fatto che il jitter periodico PJ deriva dal SSN, si compari lo spettro indicato in Figura 3 e precisamente quello della power rail in alto a sinistra con quello immediatamente sotto indicativo del TIE. La spuria di ampiezza notevole che si manifesta sulla stessa frequenza in entrambi gli spettri indica la correlazione tra PJ e il SSN che ne è causa.

Figura 3: (a) Spettro della power rail e (b) spettro TIE/jitter

Conclusioni

Signal integrity (integrità del segnale dati) e power integrity (delle linee di distribuzione dell’alimentazione o PDN) sono legate a doppio filo. Ogni elemento circuitale del layout, ogni aspetto legato ai componenti e ai connettori e persino alla scelta del package si lega a possibili conseguenze sulla PDN. L’impatto è sulla impedenza equivalente della stessa e le cui alterazioni a loro volta impattano sulle tensioni delle linee di alimentazione e sulla stabilità del piano di massa.

Il classico diagramma ad occhio ci dice moltissimo in merito alla integrità del segnale e alle cause del jitter, ma non ci aiuta nell’isolare concause legate all’effetto sul jitter delle linee di alimentazione.

Per questa ragione è opportuno non considerare più come discipline e competenze separate quelle legate alla Signal integrity e quelle legate alla power integrity, ma osservare il problema da una doppia angolazione risulta essenziale per una buona pratica di progettazione.

Lee è specializzato nei settori Embedded, Power e Automotive. Con oltre 20 anni di esperienza nel settore Test & Measurement, ha ricoperto una moltitudine di ruoli nel settore delle telecomunicazioni mobili, dell’elettronica e dell’energia, Lee ha una vasta conoscenza di come le moderne soluzioni di test possano aiutare i progettisti di oggi a creare i prodotti di domani.

Lee è specializzato nei settori Embedded, Power e Automotive. Con oltre 20 anni di esperienza nel settore Test & Measurement, ha ricoperto una moltitudine di ruoli nel settore delle telecomunicazioni mobili, dell’elettronica e dell’energia, Lee ha una vasta conoscenza di come le moderne soluzioni di test possano aiutare i progettisti di oggi a creare i prodotti di domani.